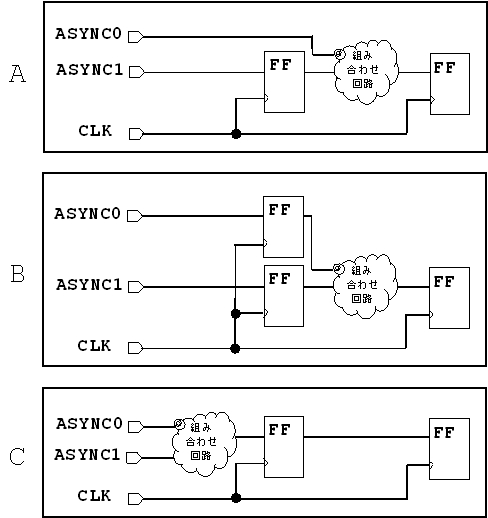

回路図(下)の後段のFFの出力には、メタ・ステーブルが発生する可能性がある。その発生確率を順に並べた正しい組み合わせはどれか。ただし、クロック(CLK)の周波数は50MHzで動作しているものとし、入力ASYNC0,ASYNC1には、CLKとは異なるクロックで駆動されるFFからデータが非同期で入力されるものとする。

< 発生確率 >

高 ← → 低

1. A,B,C

2. A,C,B

3. B,A,C

4. C,A,B

5. C,B,A

解答と解説はこちら

* 解答と解説を見るには有料サービス「Tech-On!プレミアム」の加入が必要です。「Tech-On!プレミアム」の詳細はこちらから。