ピックアップ

-

ニュース解説

TSMCもオングストローム世代へ、1.6nmプロセスを2026年に生産開始予定

-

勝村幸博の「今日も誰かが狙われる」

生成AI悪用で脆弱性を突く「自律サイバー攻撃」、GPT-4利用なら成功率87%

-

-

建設業界マンスリー・アーカイブス

原因は安藤ハザマ、法面崩壊/また設計ミス、パシフィックコンサルタンツ/築地市場跡地に5万人スタジアム建設へ

-

月面経済圏

ispaceが日米で月面着陸機開発中、26年以降は年複数回輸送

-

-

ニュース解説

メタがMR用OSを外部提供で生態系拡大、クリエーター用生成AIツールも

-

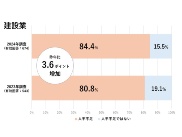

ニュース解説:建築・住宅

8割超の建設会社が正社員不足と回答、東京商工リサーチが調査

-

-

技術トップに聞く

「健全な棚上げ」で知見を未来に送るミネベアミツミ、DXでさらに強化

-

売上高1兆円間近、大塚商会の研究

「どぶ板の踏み方が大手とは違う」、社長が明かす大塚商会の実像

-

ニュース

-

TISは新中計で成長投資に1000億円、M&Aは2倍強の700億円に

TISは2024年5月8日、2027年3月期を最終年度とする新中期経営計画「Frontiers 2026」を発表した。新中計では3年間で約1000億円の成長投資を掲げた。内訳…

-

N-BOXが9カ月連続の首位、24年4月の新車販売

日本自動車販売協会連合会(自販連)と全国軽自動車協会連合会(全軽自協)が2024年5月8日に発表した同年4月の車名別新車販売台数(速報値、以下同じ)によると、登録車(乗用車)…

-

グリコ、システム障害の影響で連結売上高を150億円下方修正

江崎グリコは2024年5月8日、新基幹システムの障害によってチルド食品の出荷を停止している影響で、2024年12月期連結売上高を当初予想よりも150億円下方修正すると発表した…

トピックス

-

日経クロステック編集部おススメ

ニデックの新経営体制、世界をどう攻めるか

-

情報技術マンスリー・アーカイブス

IT大手2024年春闘/待ったなし!物流2024年問題/みずほ、なるか4度目の正直

-

先端技術マンスリー・アーカイブス

日産サクラ発売直前の悪夢、認証試験でNG/「磁石の力で鮮度保持」に専門家は沈黙/三菱電機がグラフェンで撮像素子を革新

-

建設業界マンスリー・アーカイブス

原因は安藤ハザマ、法面崩壊/また設計ミス、パシフィックコンサルタンツ/築地市場跡地に5万人スタジアム建設へ

-

知ったかぶりをする前に読んでおきたい「IT基本用語辞典」

-

仕事に役立つ! IT・電機・製造・建築・土木の用語集&Excel・Linux・ネットワークのコマンド集

-

ぜひお申し込みください「日経クロステック登録会員(無料)」の特典を紹介

-

有料会員は全記事読み放題!見たい記事が必ず探せる「日経クロステック活用ガイド」

特設サイト

日経クロステック/技術メディアの本

-

2024-25年版 技術士第二次試験 建設部門 最新キーワード100

技術士試験の最新の出題内容や傾向を基に23-24年版を大幅に改訂。必須科目や選択科目の論述で不可...

-

実践 建設カーボンニュートラル

建設事業の脱炭素化の取り組みを網羅した初の書籍。材料、設計、施工、供用、解体の“建設ライフサイク...

-

図解 木造住宅トラブルワースト20+3 「雨漏り事故」「構造事故」の事例から学ぶ原因と対策

木造住宅のトラブルを「雨漏りワースト20」と「構造ワースト3」として類型化。原因と対策と損害額が...

-

東京大改造2030 都心の景色を変える100の巨大プロジェクト

建築や土木の専門記者が取材した、一歩踏み込んだ東京の再開発プロジェクトを豊富な写真や図面で紹介し...

-

一級建築士矩子と考える危ないデザイン

住宅や建築物で起こる身近な事故と背景、効果的な防止策を人気建築漫画「一級建築士矩子の設計思考」の...

-

ソフトバンク もう一つの顔 成長をけん引する課題解決のプロ集団

ソフトバンクにはモバイルキャリア事業以外のもう一つの顔が存在する。本書ではキーパーソンへのインタ...

注目のイベント

-

日経クロステックNEXT 関西 2024

2024年5月16日(木)~5月17日(金)

-

【5月16日】ハイパーバイザーの基本を徹底解説、参加者全員にプレゼント進呈

2024年5月16日(木)

-

日経ビジネスCEOカウンシル

2024年5月16日(木)17:00~19:50

-

WEURO DIVERSITY & INCLUSION FORUM

2024年5月17日(金)13:00~17:30(予定)

-

VUCA時代に勝ち残る戦略的サプライチェーン構築に向けて

2024年 5月 24 日(金) 10:00~16:20

-

人手不足を乗り越える 日本の産業界成長のシナリオ2024

2024年5月30日(木)10:20~17:45

-

人的資本経営版:日経ビジネスLIVE 2024 Spring

2024年6月3日(月)~6月5日(水)

-

DX Insight 2024 Summer

2024年6月4日(火)、5日(水)

-

付加価値ある意匠デザインを実現するものづくり技術2024

2024年6月7日(金)10:30 ~ 17:00

-

WOMAN EXPO 2024

2024年6月8日(土)10:00~17:30

注目記事

注目記事

特設サイトアーカイブ

日経クロステック Special

What's New!

IT

- ウェルビーイング経営を実践するためには

- Webサイト運営の新手法「サイト群管理」

- AI活用を加速するストレージの要件は

- 経営の見える化を目指すマイナビの挑戦

- PayPay銀行、新時代の銀行インフラ

- 生成AIとサイバー攻撃/重要な4つの観点

- “新しい働き方”にふさわしいPCとは?

- システム運用を劇的に効率化するには?

- 【生成AI事例】デジタルで現場をDX化

- 「クラウド時代のあるべき運用」を熱く議論

- 業務や役割に応じた「社員に最適なPC」

- 生成AI活用へ「待ったなし」成功の秘訣

- 目指すは相互に行き来できるマルチクラウド

- 医療セキュリティ対策の鍵はSaaS化?

- 「サーバ―」部門満足度トップ企業に訊く

- NTTドコモ支援の実践型教育プログラム

- 大教大とマウスパソコン教室の在り方を研究

- ジェイテクトエレクトロニクスのDX事例

- 欧州トップ企業語る日本のセキュリティー

- ビジネスPC、ITデバイス購買DXを推進

- 生成AIの活用の鍵は「内製とアジャイル」

- AIと自動化でエンジニアの能力を解き放て

- 専門家が斬る日本の意識と対策の現状は?

- イノベーションの起爆剤

- 守りながら攻める“製造DX”の方法論とは

- ランサムウエアから診療データはこう守る

- 最新サーバーに学ぶ熱設計の最前線

- PC管理の課題を課題をまるごと解決

- 日本語に強い「和製生成AIモデル」が誕生

- 動画解説>生成AIからDX変革まで

- 生成AI活用でSAP BTPの価値が進化

- ServiceNowでDXを加速≫方法は

- SAPプロジェクトの全体像をいかに描くか

- 先端教育の現場で活躍する大学副学長が使い続けるレッツノート