キヤノンと東芝が,共同で開発を進めたディスプレイで「SED(Surface conduction Electron emitter Display)」。2004年9月14日,両社はパネルの開発,生産,販売を目的とした合弁会社を10月に設立すると発表した。

SEDは,電子源から出た電子を蛍光体に当てて発光させるFED(field emission display)の一種である。従来のCRTが,一つの電子源から出た電子を走査させて一画面にするのに対し,FEDは各画素に電子源があり,電子を走査させる必要がない。一般的なFEDは,電子源が円錐形状で半導体プロセスが必要となるが,SEDは平面状でインクジェットなどの厚膜プロセスで形成できる。このため,従来のFEDに比べて低コストで製造できる。一部の製造装置はPDP向けを流用することが可能である。

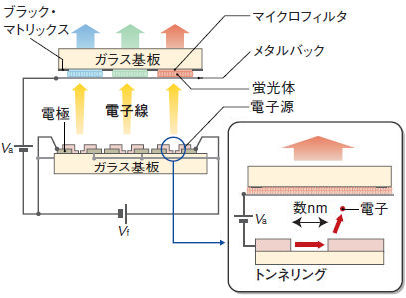

SED の動作原理は次の通り(図1)。電子源となる陰極側は,亀裂(スリット)の入ったPdO膜で形成している。この亀裂間に電圧をかけるとトンネル電流が流れ,電子が真空中に引き出される。その電子を電圧で加速し,陽極側のR(赤),G(緑),B(青)に対応する蛍光体に当て,発光させる。亀裂の間隔は数nm と狭いことから,電子を引き出す駆動電圧は10数Vと,CRTの約50V,PDPの約80Vに対して低い。このため,「駆動LSIを低コストで構成できる」(キヤノン)と言う。

図1●SEDの基本的な構造 駆動電圧Vfは10数V,加速電圧Vaは10kVと比較的低い。試作した36型パネルの場合,1枚のガラス板厚は2.8mm,ガラス板間は約2mmである。寿命は蛍光体に律速し,輝度の半減期で3万時間とCRT並みであるという。キヤノンと東芝のデータ。

表示画面は,自発光ディスプレイの特徴をそのまま踏襲する。利点として暗い環境でのコントラスト(暗コントラスト)が高い。黒表示の時に,液晶パネルのバックライトの光漏れやPDPの予備放電のような余分な光を出さないためである。試作した36型(対角91cm)パネルの暗コントラストは8600:1とCRTとほぼ同等である(図2)。弱点として,各画素が独立して発光するため,輝度バラつきが生じやすい。これに対しては「製造プロセスによる均一化と,回路技術によるバラつき補正で解決している」(キヤノン)とする。

図2●試作した36型SEDパネル ワイドXGA。ピーク輝度は300cd/m2,全白輝度は260cd/m2。消費電力は最大160W,ニュースなど明るい表示の時は120~140W(PDPの1/3,液晶パネルの2/3),映画など暗い表示の時は90~100W(PDPの1/2,液晶パネルの1/2)といずれもPDP,液晶パネルより低いという。本誌が撮影。