以下では,EMCを考慮した機構設計や回路設計の具体例や開発プロセスを紹介する。

技術やナレッジをデータベースに登録

EMC設計は,「発生源でいかに低減させるか,伝播系でいかに減衰させるか」が重要であると述べたが,伝播系での減衰は機構設計で実現していくことになる。機構設計の方針は,放射エミッションに対してはシールドの網羅度向上,伝導エミッションに対してはグラウンド・インピーダンスの低減がベースになる。具体策は,図18中の(1)~(8)のように,コネクタ・シールドの設置やねじによる基板と筐体の共締め,プリント基板のグラウンド全体のインピーダンスを下げるためのオンボード・コンタクトの設置,機能別にキャビティ分割した構造の採用などである。これらの方策を構想段階から取り入れ,設計の後戻りを防止する。この構想設計をルール化し,ものづくり前のレビューと,ものを作ってからの現物確認の両方で,着実に具現化していく。

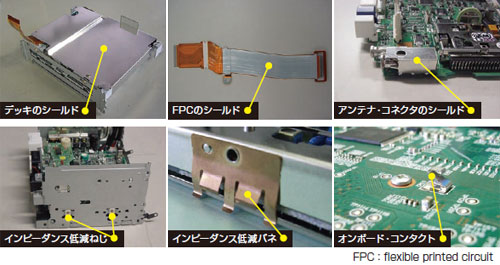

実際の機構設計について,シールドの事例とインピーダンス低減の事例を写真で紹介する(図19)。これらは構想段階であらかじめ設計する際,不要な場合に後で外せるように配慮しておく。

次にプリント基板のアートワークにおけるEMC設計の事例を紹介する(図20)。これらは,当社内に蓄積しているナレッジ・データベースの一部である。(1)は電源周りの配線であるが,ベタのグラウンドやビア・ホールの設置法を具体的に示している。(2)はデカップリング・キャパシタをループ面積が最小になるように配置すること,(3)はシリアル通信回路の信号のリターン・パスを近傍に確保すること,(4)は発振回路のパターンを配線の距離が最小になるようにすることを示す。これらのナレッジは,誰が見ても分かるように,極力,写真やスケッチで残している。

同じくプリント基板のEMC設計であるが,ここではメモリ・バスのアートワークについて例示する。高速で論理作動を可能とするためのタイミング設計を行いながら,不要輻射の要因となるオーバーシュートの防止を目指す。パターン上を走るクロックの周波数が1GHzに迫っているので,信号の反射による悪影響を防止するために線路のインピーダンス・マッチングは必須である。

また,高速信号を扱うので,基板上での信号の伝達遅延も重点的に管理しなければならない。例えば配線長の1cmの差は,プリント基板上では通常,遅延時間にして67psの差となって現れるため,配線長を誤れば論理作動に致命傷を与えかねない。プリント基板が出来上がってから発覚すると,作り直しに1~2カ月もの時間がかかってしまう。従って,シミュレーションが必須となるわけである。この事前シミュレーションと実機完成後の波形を比較すると,設計で先回りして配慮すれば狙った波形を確保できることが分かる(図21)。