3次元チャネル構造のCMOSトランジスタに、不揮発性のキャッシュ・メモリ、3次元セル構造のストレージ向け新型不揮発性メモリ─。2012年6月に米国ハワイで開催された半導体製造/回路技術の国際学会「2012 VLSI Symposia」には、「3次元」や「不揮発」といったキーワードが目白押しだった。既存技術を超えた低電力化・低コスト化を目指す。

「普通の会社だったら、こんな大きな変更は怖くてできない」──。半導体技術の国際会議「2012 VLSI Symposia」に出席したある技術者は、米Intel社が発表した3次元チャネル構造のトランジスタ「Tri-Gate」について、このように語った。

半導体の歴史の中で、論理LSI向けのCMOSトランジスタが量産レベルで3次元チャネル構造に変わったのは今回が初めてである。チャネル構造が変わると、チップ設計環境などのエコシステムを全面的に見直さなくてはならない。そうまでしてIntel社がTri-Gateの導入に踏み切ったのは、従来技術の延長で微細化を続けることが非常に難しくなってきているからだ。

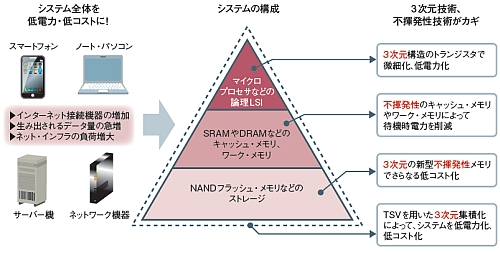

今回のVLSI Symposiaでは、Tri-Gateに代表される大胆な新技術が相次いだ。それらを表すキーワードは「3次元化」と「不揮発化」である。3次元のデバイス構造と不揮発性のメモリ技術などによって、喫緊の課題になりつつあるシステム全体の低電力化・低コスト化を目指す。