DDR2 SDRAMの検討が始まったのは2000年ごろ。DDR SDRAMの策定作業は難航したが、これはIntelがDirectRDRAMを推したためだ。IntelはDDR2の標準化に協力的で、作業は順調に進んだ。ところが、2002年を想定していた完了間際でどんでん返しがあった。その結果最初の標準規格の発行が2003年にずれ込んだ。

この要因は3つ。まず参加企業が土壇場に出した追加要求に対応したこと。次にIntelの要求でDDR400を標準化したため、DDR2-533の策定が当初から求められたこと。最後にDRAMの価格競争が一段落していたため、DDR2対応で利益率の高いメモリーで差別化を図る必要が薄れたことがある。2003年の製造技術では、DDR2-533への対応がやや難しかったことも一因だろう。結果としてDDR2 SDRAMの本格出荷は2005年に入ってからとなった。

内部でクロックを半減

プリフェッチで倍速に

技術的には、DDR SDRAMに比べ転送速度を2倍にした。メモリーセルに供給するベースクロックの4倍の速度でデータを転送する。このために、「4nプリフェッチ」を採用した。また、駆動電圧を2.5Vから1.8Vに変更し、「ODT(On DieTerminator)」を搭載した。

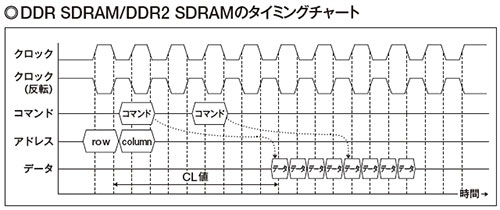

DDR SDRAMの2倍の速度で転送するため、独特のタイミングの取り方を採用した。タイミングチャートを見る限り、DDRSDRAMとDDR2 SDRAMは変わらない(図1)。例えばDDR2-400の場合、供給されるクロックは200MHzで、データは400MHzで転送される。DDR2 SDRAMでは、内部でクロックを半分に落としてベースクロックとする。半分に落としただけではクロックに合わせてデータを返せないので、プリフェッチの量をDDR SDRAMの2nから4nに倍増させた。