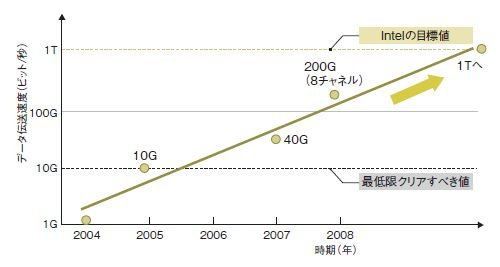

「Siフォトニクスが,Tビット/秒のコンピューティング技術のカギを握る」(米Intel Corp. Fellow,Corporate Technology Group Director,Photonics Technology LabのMario J. Paniccia氏)。受発光デバイスや光導波路をSi基板に集積する“Siフォトニクス”の開発が,大きく動き始めた。Si基板に作製したデバイスの性能が,ここ2~3年間で飛躍的に高まっている(図1)。光配線に求められる数十Gビット/秒のデータ伝送速度への対応が見えてきた。

早ければ2010年代半ばから,ボード間やチップ間を結ぶ光配線へのSiフォトニクスの適用が始まる。2010年代後半には,LSIチップの内部へ光配線を導入する動きが始まりそうだ。

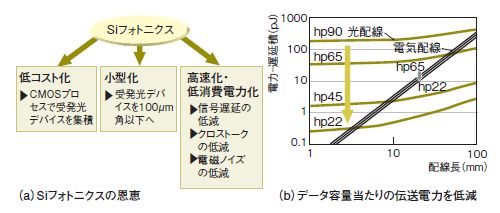

Intelのような大手LSIメーカーが当面の開発課題に掲げているのが,光配線を構成する受発光デバイスや導波路をSi基板上に形成する技術である。 CMOS工程で集積する手法や,実装工程で集積する手法がある。これにより,受発光デバイスや導波路を個別部品としてプリント基板に実装する方式に比べて,光配線モジュールの小型化や低コスト化が可能になる(図2)。

例えば,光電変換を担う受光デバイス(フォトダイオード)の実装面積は,一般に1mm角を超える。これをSi基板上のデバイスとして形成できれば,100μm角以下へ小型化できる。コストについては,「LSIで培った低コストの製造技術が生きる」(IntelのPaniccia氏)。

LSIメーカーが光配線技術に手を伸ばし始めたのは,光配線がLSIチップ内へ浸透する時代がやがて訪れるからだ。LSIのグローバル配線を光配線で置き換え,チップ内の信号伝送を高速化および低電力化する。現行のメタル配線は,微細化に伴って寄生抵抗が増大し,データ転送時の消費電力が大きくなる。このため,「20GHz以上への対応は難しい」(東北大学教授 工学研究科バイオロボティクス専攻の小柳光正氏)。

こうした背景から,半導体先端テクノロジーズ(Selete)はLSIチップ内に向けた光配線技術の開発を進めている。2015年ごろに量産化する「ハーフ・ピッチ22nm世代での実用化を目指す」(Selete 第四研究部 NSIプロジェクト 光配線プログラムプログラムマネージャーで,NEC ナノエレクトロニクス研究所 主席研究員の大橋啓之氏)。

Siの弱点を克服する

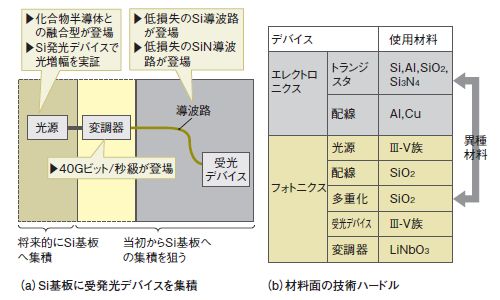

Siフォトニクスの実用化に向けた技術ハードルは,受発光デバイス向け材料としてのSiの弱点を補うことにある。Siは,受発光デバイス向け材料としては化合物半導体に比べて劣る場合が多いからである(図3)。

まず,Siは間接遷移型注1)のバンド構造を持つことから自発光を得にくい。このため,Si基板にSiレーザー光源を形成することが「極めて難しい」(東京大学大学院工学系研究科 教授マテリアル工学専攻の和田一実氏)。さらに,長波長の光に対して透明または吸収係数が小さいため,長波長帯の受光デバイスを実現しにくい。

注1)間接遷移型では,伝導帯の電子が価電子帯の正孔と再結合するために運動量が必要となる。この結果,再結合による発光が起こりにくい。

ここ2~3年で,こうした課題を克服する技術が相次いで登場した。光配線を構成する(1)光電変換(受光)デバイス,(2)導波路,(3)変調器,(4)光源(発光デバイス),のいずれにおいても,Si基板へ搭載する道が開けてきた。