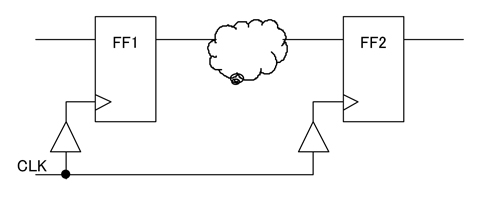

図のフリップフロップFF1,FF2において、

・要求するセットアップタイムを満たすかどうかは、

クロック周期に依存する

・要求するホールドタイムを満たすかどうかは、

クロック周期に依存しない

なぜホールドタイムの方は、クロック周期に依存しないのか。その理由を以下の手順で説明せよ。

< 回路構成図 >

(1)「ホールドタイムとは~」の書き出しで、まずホールドタイムとは 何か

を説明する。

(2)続いてホールドタイム違反がクロックの周期に依存しない理由を、

FF2を対象に説明する。

解答と解説はこちら

* 解答と解説を見るには有料サービス「Tech-On!プレミアム」の加入が必要です。「Tech-On!プレミアム」の詳細はこちらから。