発生した問題

大手電気メーカーA社のGさんは,家電機器のハードウエア設計を担当しており,長年にわたり,1チップ・マイコンを利用して数々のヒット商品を開発してきました。このマイコンはプロセサをコアとして,ROM/RAM,タイマ,DMA(direct memory access)コントローラ,液晶ディスプレイ・コントローラなどを搭載したものでした。Gさんはその実績が認められて,最近DVDレコーダーの電子回路設計のリーダーに抜擢されました。

この分野は競合メーカーが多く,常に熾烈な開発競争を繰り広げています。そこで従来の経験を最大限に生かし,これまで非常に良く対応してくれた半導体メーカーのマイコン応用技術の担当者と一緒に開発を進めることにしました。Gさんはこの担当者と一緒に検討し,DVDレコーダーに必要な専用機能回路ブロックを1チップ・マイコンに搭載することを決めました。マイコンのサンプルはスケジュール通りに出来上がりました。

ところがその後の開発は難航しました。チップ評価の段階で多くの問題が続出したのです。例えば,チップ内のPLL(phase-lock loop)が雑音のためにロックできないという誤動作が発生しました。さらに致命的なことに,動画像をきちんと再生できませんでした。

原因と対策

動画像の問題は,チップ内のシステム・バスで伝送できる動画像のブロック転送量などが不足したために発生しました。今回のシステム・バスは,DVDレコーダーに必要なデータ転送負荷のピーク値に耐えられるスループットがなく,さまざまなデータの競合を調停するバス・インタフェース機能も不十分でした。

これは,1チップ・マイコンの従来のシステム・バスをそのまま使ってしまったからです。従来は動画像のような高速のデータ転送に必要な処理をしていませんでした。

そもそも1チップ・マイコンに対するニーズや仕様の検討が足りませんでした。また,設計もずさんで,その場しのぎで回路ブロックを加えたので,システム・バスや電源/接地などの配線が,チップ上をはい回ってしまいました。これらがさまざまな雑音を拾って,PLLに悪影響を与えました。Gさんは,このような高い性能が要求される機器を作った経験がなく,いわゆるSoC(system on a chip)を作る手法を知らなかったのです。

結局,新しい高性能1チップ・マイコンの開発は中止せざるを得ませんでした。このため,実績のある半導体メーカーのSoC開発部門を選択して,きちんとしたSoC開発手法に切り替えました。

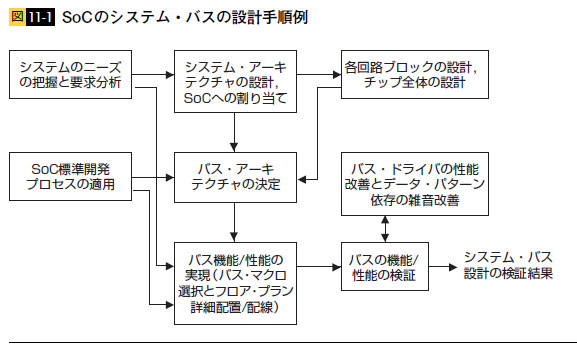

ここでは次の8点に注意しました(図11-1)。細かい設計に入る前に,システム・アーキテクチャやバスの設計を行い,チップ内に“背骨”を通すことに注意しました。

(1)システムのニーズの把握と要求分析。例えば,業務要求事項(フローとアクティビティ:ここではユーザーの操作と機器の動作の流れ)や,ユーザー要求事項(主に操作と表示の仕様)といったことがポイントでした。もちろん,動画像などのリアルタイム性能は必須の仕様です。

(2)SoC標準開発プロセスの適用。半導体メーカーのSoC開発部門やEDAベンダーが推奨している実績のあるSoC標準開発プロセスを利用しました。方式設計や検証/妥当性評価が最も重要でした。

(3)システム・アーキテクチャの設計とSoCへの割り当て。具体的に今回のDVDレコーダーでは,十分な性能を得やすいように,SoCチップに割り当てる機能を以下のように決めました。静止画像と動画像の圧縮/伸長。DVDやCD,ビデオ・テープへのダビング制御。HDDへの記録。ディスプレイへのデータ転送。外部とデジタル・ビデオ信号などをやりとりするシリアル通信機能(IEEE1394),複雑なリモコン操作の解読部分,各種デバイス制御機能。

(4)各回路ブロックの設計,チップ全体の設計。(3)を行ったら,SoCへ割り当てた機能を基に,チップ内部の方式設計を行います。すなわち,チップ全体の構成として,(I)各回路ブロック,(II)ブロック間インタフェース,(III)チップ外部へのインタフェース,を決定します。ここで得られた複数の回路ブロック間インタフェースとして,具体的なバス形式を選択して,次のバス・アーキテクチャを作ります。

(5)バス・アーキテクチャの決定。ここでバス・アーキテクチャとは,プロセサとメモリ間の専用のバス,高速ブロック転送用バス,システム・バスなど,組み込み機器の機能と性能を満たす階層バス構造を選択することです。

(6)バス機能・性能の実現。次の3点に特に注意します。(a)バス向けマクロの選択。半導体メーカーのSoC開発部門やEDAベンダーのバス・アーキテクチャを利用できるバス・マクロを利用します。ただし,新しいバスを開発する場合もあります。(b)フロア・プラン。要求された機能/性能やコスト,品質を満たすためのおおよその配置戦略です。例えば,プロセサやメモリ,各種の再利用マクロ,および機器メーカーが開発した専用機能回路ブロックの配置戦略を決めます。(c)詳細配置/配線。SoCのマスク設計に必要な物理的精度で,サブブロック・レベルの具体的な配置とその間の信号ライン,電源/設置ライン,各種バス・ラインの配線を行います。なお,ここでバスの遅延時間,バス・バンド幅(転送速度),雑音,ドライブ能力,インピーダンス,反射減衰量などの重要な性能の諸元は不可欠です。1チップ・マイコンのプロセサやメモリ,周辺ブロックは,半導体メーカーが独自に最適化しています。特にそれらを結び付けている内部のバスは,その半導体メーカー特有のものです。システム・バスの制御仕様もメーカーごとに異なります。開発の早い段階でこれらを明確にし,設計指針を文書化することにしました。具体的には,電子回路やSoC標準開発ライフ・サイクル・プロセスの手順書や,開発/設計手法,ヒントを盛り込んだガイドラインを用意しました。

(7)バスの機能/性能の検証。例えば,直ちに再利用できるバスや設計/検証ツールの事前調査,検討に注力しました。EDAベンダーの推奨するIPマクロ・ライブラリ,半導体メーカーの推奨するバス構造の実績を事前調査し,開発で必要なバスの機能/性能の検証に適切な評価ツールを選んで使いました。フロア・プランや具体的な配置/配線の質が高いかどうかの実績調査は,見落としがちですので注意しましょう。

(8)バス・ドライバの性能改善と,データ・パターン依存の雑音改善。これは経験がないと難しいので,半導体メーカーの推奨例の利用やトラブル事例集のコンサルティングが効果的でした。分からないことは,率直に半導体メーカーや外部コンサルタントに問い合わせました。ただし,うのみにすると破綻するかもしれないと聞いていたので,すべて自分で納得して行動するようにしました。これらのポイントを押さえることで,2回目はなんとか成功しました。

技術者必修の基本

たいていの技術者は,Gさんのように,できること,これまで実施したことを基準に考える傾向が強いものです。着実に製品を作っていくため,そういう姿勢になることも理解できます。

しかし,これまで扱ったことのない機器を作るときは,まずは機器設計や開発プロセスを,ゼロから見直してみることが不可欠です。当たり前のことですが,残念ながら設計手法や開発プロセスが確立していない企業/部門が多いのが,実情といえます。このため,ニーズからシステムの機能や性能,価格,納期,品質を順々に決定することができず,破綻してしまいます。これは,会社にとっても技術者個人にとっても不幸なことです。

設計手法や開発プロセスは,世の中に確立したものがあります。もちろん方式設計などは素人ではできませんが,手順に沿って粛々と実施すれば,新しい機器の開発も恐れることはありません。開発期間も短くなるものです。丁寧に考えれば,チップや回路ブロックが長持ちして何回も再利用できるようになります。 ここではチップ内のシステム・バス設計について述べましたが,自分で技術的,組織的な基準を作り,開発を進めれば,新しい機器を着実に効率良く作ることができるようになります。