MOS FETの特性バラつきをいかに抑えるか。これが微細化に伴う最重要課題との認識が広がってきた。そこで,デバイスの加工形状を測定する物理計測技術が欠かせなくなってきた。連載の第4回は,デバイスの物理計測とそれを活用したプロセス・モニタリングの強力な手段である測長SEMを紹介する。測長SEMによるデバイス計測技術開発の最前線のほか,設計との連携によるプロセス制御の取り組みも解説する。

杉本 有俊

日立ハイテクノロジーズ

半導体製造装置営業統括本部

事業戦略本部

LSIの微細化に伴い,製造技術の高度化と複雑化が進んでいる。リソグラフィ光源の短波長化や光学系の高開口数(NA)化,k1ファクタの低下などである。これらの変化に伴って,製造プロセスにおける加工バラつきがMOS FETの特性や歩留まりに与える影響が大きくなってきた。そこで,デバイスの加工形状を直接測る物理計測の重要性が高まってきた。

現時点で,そのための唯一の技術といえるのが測長SEMである。本稿では,測長SEMの原理とデバイス計測への応用を解説した上で,加工バラつきが電気的特性などに与える影響を紹介する。

モニタリングと寸法計測に活用

測長SEMの強みは,二つの方向に分かれ始めた計測技術の両方に対応できる点にある。その二つの方向とは,(1)プロセスの制御を目的とした高精度のプロセス・モニタリング,(2)MOS FETの製造工程管理のためのインライン寸法計測である。

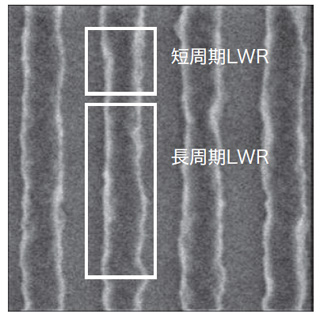

(1)高精度のプロセス・モニタリングの目的は,プロセス装置の加工条件を最適化し,その条件を維持することである。例えば,300mm径のウエーハ内やウエーハ間での加工の均一性を維持する要求に応えられる。加工の均一性評価で重要となるのは,素子内の局所的な加工バラつきを計測値から排除することである。そこで近年,局所的なバラつきの影響を受けにくい計測手法が登場してきた。測長SEMによるマクロ領域の平均化計測や光寸法計測(OCD:optical critical dimension)である。測長SEMとOCDはいずれも,重要性が高まっているデバイス断面プロファイルの管理にも利用できる。

(2)インライン管理のための寸法計測は,これまでMOSゲート幅の測定をはじめとする1次元の線幅測定が主体だった。ところが,MOS FETの微細化が進んでOPC(光学近接効果補正)を施したマスクが必要となったことで,その状況が変わってきた。OPC処理と検証のための高精度な2次元計測が必要になってきたのである。測長SEMは,この高精度な2次元計測に対応できる。

これらに加えて,測長SEMはEDA(electronic design automation)ツールを含むDFM(design for manufacturability)とのシステム化が可能である。DFMに活用できれば,測長SEMは単なる寸法測定技術から,新たな付加価値を持つ計測システムへと進化することになる。