前回に引き続き,ΔΣ型と逐次比較型のA-D変換器の各種性能を比較する。今回は,多くの技術者がもやもやしているΔΣ型のデータ変換の開始/終了の考え方や消費電流の大きさ,拡張性の高さなどに着目する。そして,従来は逐次比較型を使ってきた分野にもΔΣ型が採用され始めた例を紹介する。(清水 直茂=日経エレクトロニクス)

ΔΣ(デルタ・シグマ)型A-D変換器と逐次比較型A-D変換器において用途に応じた使い分けを考えるには,アナログ入力部とA-D変換部,デジタル出力部の三つの要素で各種性能を比較しなければならない。前回は,アナログ入力部の応答性と前置フィルタの次数,A-D変換部の分解能の限界について説明した。

今回は,A-D変換部に関しては引き続いて分解能の限界の解説に加え,データ変換の開始と終了のタイミングの違いや,変換速度と消費電流の関係について説明する。デジタル出力部に関しては,パラレル方式とシリアル方式の違いや,拡張性の高さについて論じる。最後にまとめと,性能向上の著しいΔΣ型が,これまで逐次比較型が得意とする分野において適用されつつある例を紹介する。

<A-D変換部(続き)>

分解能重視なら高次のΔΣ型

前回,ΔΣ型の分解能の限界は有効ビット数(ENOB:effective number of bits)によって決まり,オーバーサンプリングとノイズ・シェーピング,デジタル・フィルタによる高域雑音のカットといった手法を駆使することで高い ENOBを実現していることを紹介した。今回はその続きとして,ΔΣ型ではモジュレータとデジタル・フィルタの次数を高めることで,ENOBをさらに高くできることを説明する。

連載第1回で説明したが,ΔΣ型はモジュレータとデジタル・フィルタから成る。モジュレータは積分器と負帰還で構成され,入力電圧VINPに応じて “1”と“0”で構成されるビット・ストリームを出力する。ここで積分器と負帰還のペアの段数を,モジュレータの次数という(図1)。次段のデジタル・フィルタではビット・ストリームの“1”の数をカウントして,データ変換する。

連載第2回で説明したように,モジュレータの積分器と負帰還という構成は,量子化雑音NQに対して高域通過(ハイパス)フィルタとして作用する。そしてハイパス・フィルタの効果は,モジュレータの次数によって変わる。

高ENOBには高次のモジュレータ

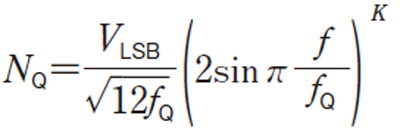

このことを端的に表しているのが,モジュレータの次数Kと量子化雑音NQの関係を示した次式である。

(NQ=量子化雑音,f=NQの周波数,K=モジュレータの次数,fQ=モジュレーション・クロック周波数,VLSB=1LSBを電圧換算した値)