無線通信回路の周波数シンセサイザや,マイクロプロセサの高速クロック生成回路において,必須の回路がPLLである。通常はアナログ回路で実現する。このPLLを,すべてデジタル回路で構成するという設計コンセプトが「ADPLL」だ。実際にADPLLを利用した回路の研究開発を進めている群馬大学の小林氏らが,ADPLLの意義や,構成について解説する。(日経エレクトロニクス)

最近,回路設計においてADPLL(all digital phase-locked loop)というキーワードを聞くことが多くなってきた。ADPLLは,その名の通り,すべてをデジタル回路で構成したPLLである。特に,微細な設計ルールを用いて製造するCMOS製システムLSIに適した技術と言える。

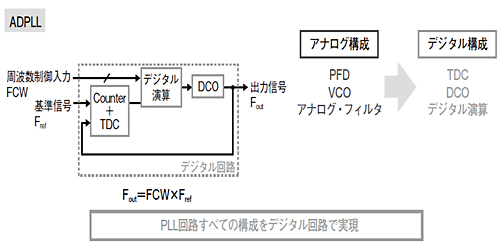

ADPLLは,元米Texas Instruments Inc.(TI社)のBogdan Staszewski博士によって提案された位相同期回路方式である(図1) 1)。

1)Staszewski,R.,Balsara,P. All-Digital Frequency Synthesizer a Deep-Submicron CMOS. Wiley Interscience. 2006.

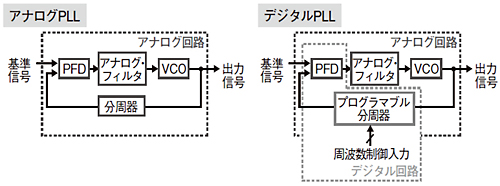

無線通信回路の周波数シンセサイザにおけるキー・テクノロジーであることなどから,各国の大学や企業で活発に研究が進んでいる。これまでも「デジタルPLL」と呼ばれるものがあったが,実際にはかなりアナログ回路が残っていた(図2)。

ADPLLの研究開発には,PLL回路技術に加えてデジタル信号を処理する知識が不可欠である。また,ADPLLの設計思想は,システムLSI内部のほかのアナログRF回路の設計にも示唆を与えるものである。

PLL回路を専門としている日本人の技術者や研究者の方に聞くと,「ADPLLは今後必要な技術だが,直近の仕事で手いっぱいで,なかなか着手できない」という声が多い。このため,ADPLLへの理解が不十分で,自社で取り組む余裕がないことから設計会社に開発を委託する,といった例が多いという。