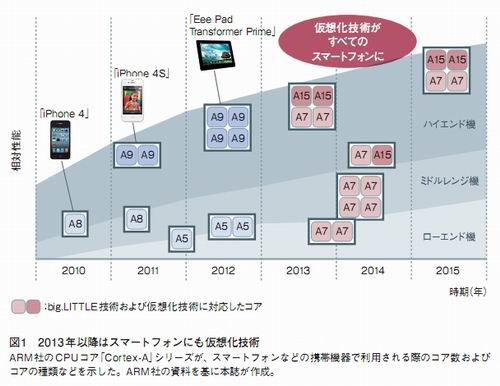

デュアルコアやクアッドコアの搭載が当たり前となってきたスマートフォンやタブレット端末。 次世代のアプリケーション・プロセサのCPUコアはどうなるのか。 同分野で支配的なシェアを握る英ARM社が 今後数年間のマルチコア技術のロードマップを明らかにした。 大小の異なるコアを組み合わせることで、高性能と省電力を両立させる戦略だ。 そして異種コアの併用は、モバイル分野に仮想化技術を導入する礎にもなる。

スマートフォンやタブレット端末などに向けたCPUコアを手掛ける英ARM社が2011年秋に発表したコア「Cortex-A7」には、一見すると奇妙な機能が盛り込まれている。

Cortex-A7は、価格が100米ドル未満という廉価版のスマートフォンに向けられたCPUコアである。低消費電力化や低コスト化を最重要視して設計されており、その電力効率は米Apple社の「iPhone 4」に搭載されているARM社の既存のCPUコア「Cortex-A8」と比べて約5倍にまで高められている。

そんな「エコ運転」に徹したコアであるCortex-A7に、実はモバイル分野ではおよそ不要と思われる高度な技術や機能が満載されている。仮想化支援技術、主記憶向けのECC機能、40ビットの物理アドレス拡張(LPAE:large physical address extensions)などだ。

電力効率の向上や回路面積の削減を徹底しようと思えば、廉価版スマートフォン向けのCortex-A7に、仮想化支援技術などは必要ないようにも思える。なぜARM社はこうした機能を同コアに実装したのか。

Cortex-A7に高度な機能が実装されているのは、将来のスマートフォンにおいて高性能と省電力という相反する特性を両立させる「big.LITTLE」と呼ぶ技術を実現するためだ。