いよいよ,光通信技術がプロセサ・チップ間やプロセサ・コア間のデータのやりとりに用いられる可能性が高まってきた。米IBM Corp.が,光の送受信回路と電気回路をCMOS技術で1チップ上に集積する技術「CMOS Integrated Silicon Nanophotonics」を開発したからだ。IBM社は今回,実用化の目標時期も示した。同社が2017~2018年に開発予定の,浮動小数点演算性能が1018FLOPS(エクサ・フロップス)のスーパーコンピュータ(エクサ機)向けのプロセサに利用する予定という。

実現すれば,プロセサ・コア内部を除くデータ伝送用配線を光通信技術で実装できるようになる。そのインパクトは,スーパーコンピュータに限らず,さまざまなエレクトロニクス機器に対しても非常に大きなものになる。

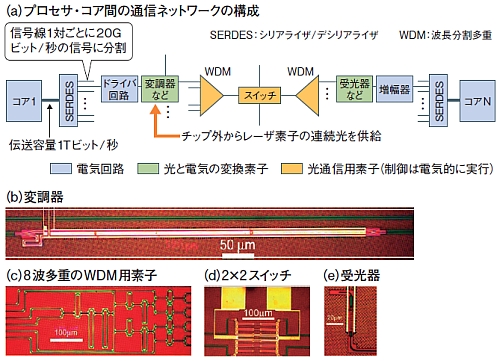

WDM技術で配線数を大幅削減

IBM社は,現時点で最速のスーパーコンピュータに比べて演算性能が約1000倍のエクサ機を実現するためには,プロセサ・チップ間やプロセサ・コア間のデータ通信の光化が不可避と考えている。「人間の脳もプロセサに相当する灰白質と,通信ネットワークに当たる白質の両輪がそろって初めて有効に機能する。白質のデータ伝送速度が低くては,せっかくの灰白質を生かせない」(同社,Silicon Integrated Nanophotonics,ManagerのYurii A. Vlasov氏)。電気に代えて光を用いる最大の理由は,光通信分野におけるWDM(波長分割多重)技術の適用により物理的な配線数を大幅に減らせることにあるという。