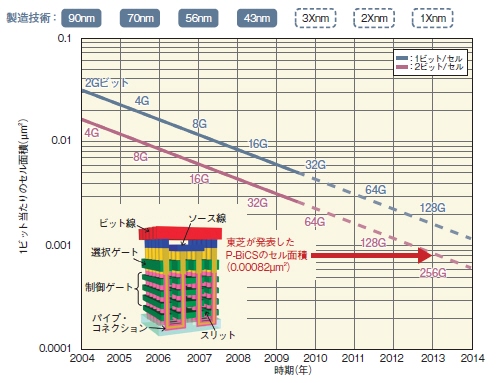

「現行のNANDフラッシュ・メモリの微細化はどこまで続くのか」。この問い掛けに対して,NANDフラッシュ・メモリの2大メーカーであるSamsung Electronics社,東芝はそろって「2Xnm世代」と答えた。2009年6月に開催された半導体製造/回路の国際会議「2009 Symposia on VLSI Technology and Circuits」のランプ・セッションでのひとコマである。2Xnm世代の量産は2011~2012年に始まることを考えると,早ければ2013年ごろには微細化に代わる新たな大容量化手法が必要になる。その有力候補が,メモリ・セルを3次元方向に縦積みする,いわゆる3次元セル技術。この技術開発が加速し始めた。

NANDフラッシュ・メモリの低コスト化/大容量化はまだまだ進みそうだ。少なくとも,2011~2012年に量産が始まる2Xnm世代の 64G~128Gビット品は,従来技術の延長線上で実現できるとの見方が多い。さらに,将来のTビット領域のNANDフラッシュ・メモリに関しても,これまで通りのペースで低コスト化が進む可能性が出てきた。

実現のカギを握るのは,3次元セルと呼ぶ新技術である。この技術がTビット領域を狙っていることは,NANDフラッシュ・メモリ最大手の韓国 Samsung Electronics Co., Ltd.が開発中の3次元セル技術「TCAT(terabit cell array transistor)」の名称からも明らかである。

3次元セルは,これまで1層構造だったメモリ・セルをチップ上で積層することで,製造コストを低減する技術。チップを積層する場合には積層数に比例してコストが増えてしまうが,3次元セルは積層数を増やしてもコストの上昇を最小限にできる。このため,積層数を増やすことで,旧世代の微細化技術を使いながら1ビット当たりのコストを劇的に下げることが可能となる。

これまでNANDフラッシュ・メモリは微細化を進めることで低コスト化/大容量化を達成してきた。しかし,2Xnm世代を境に,微細化のペースが鈍る,あるいは止まる可能性がある。3次元セルは,その限界を突破できる可能性を秘める。2009年6月に京都で開かれた半導体技術の国際会議「2009 Symposia on VLSI Technology and Circuits」では,3次元セルの技術発表が相次いだ。

3次元セルで32Gビット品を試作

初期の3次元セル技術は,積層数とほぼ比例してコストが増えてしまう問題があった。1層ごとに微細加工が必要だったためである。これに対し,2007年に積層数が増えてもコスト上昇を抑制できる「BiCS(bit-cost scalable)」と呼ぶ3次元セル技術を東芝が開発し,大きな注目を集めた。この技術は,多数のセルを形作る多結晶Si電極と層間絶縁膜を交互に積み重ねた後,一括で上層から下層まで貫通する孔を開け,その内部に酸化膜やSi電極を埋め込むというもの。このため,積層数が増えても製造工程数はそれほど増えない。

今回東芝は,このBiCSに改良を加え,実際の製品に近い容量を持つ32GビットのNANDフラッシュ・メモリを試作した。16段積層のセルと,2ビット/セルの多値動作を組み合わせることで,60nm世代の製造技術を使いながら1ビット当たりのセル面積を0.00082μm2に縮小した。このセル面積は,3次元セルを使わない場合(2ビット/セル品)には20nm世代まで微細化しないと得られない値である。なお,東芝はこの発表により,論理LSIやアナログなどの優れた論文がひしめいた「2009 Symposium on VLSI Technology」の全採択論文80件の中で,最高得点を獲得している。