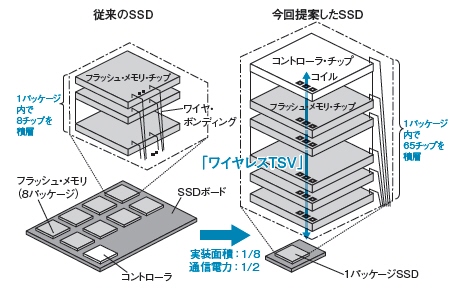

NANDフラッシュ・メモリの微細化や多値化の技術的な障壁が高まる中で,相対的に重要性を増しているのが,チップの3次元積層技術である。慶応義塾大学は65 枚ものチップを無線で積層接続できる技術を開発した。256GバイトのSSDを1パッケージに収められる。ワイヤ・ボンディングを使った従来方式に比べて高速化や低電力化が可能であり,追加コストも必要ないという。(本誌)

黒田 忠広

慶応義塾大学 理工学部 電子工学科 教授

HDDの代替を狙う半導体ストレージ装置のSSD(solid state drive)。現行の標準的な構成のSSDでは,内部でNANDフラッシュ・メモリを8枚積層したLSIパッケージが8個と,コントーラ・チップ1枚の計 65枚のチップをボード上に搭載している。我々は,これらすべてのチップを一つのLSIパッケージ内に集積できるチップ間無線通信技術「ワイヤレスTSV(Through Silicon Via)」を開発した。LSIの配線で作ったコイルの磁界結合を利用し,積層したチップ同士を無線で接続する。

4Gバイト(32Gビット)のフラッシュ・メモリを64枚用いたとすると,256GバイトのSSDを1パッケージで実現できることになる。SSDの体積は現行品の1/8以下になり,財布に入れて持ち運ぶことも可能になるだろう。パソコンや携帯電話機,デジタル民生機器などに搭載すれば,ユーザーの使用環境を手軽に持ち運べるようになるかもしれない。

ワイヤレスTSVは,チップ間の通信電力が従来のワイヤ・ボンディングに比べて1/2と低く,伝送性能も,チップに貫通ビアを形成する従来のTSV並みに高い。しかも,追加のコストはほぼゼロである。NANDフラッシュ・メモリの微細化や多値化の技術的障壁が高まる中で,ワイヤレスTSVはますます重要になると考えられる。