本記事は、日経WinPC2013年6月号に掲載した連載「PC技術興亡史」を再掲したものです。社名や肩書などは掲載時のものです。

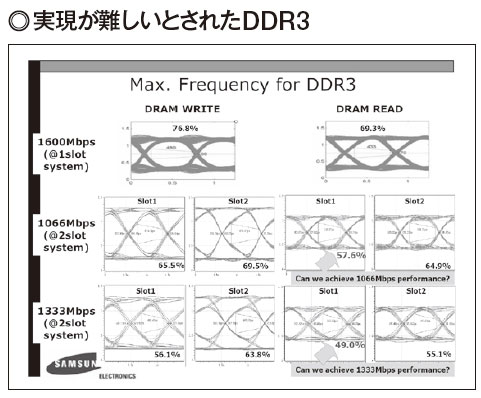

DDR3 SDRAM規格の検討は2005年に始まった。最初の標準規格となったJEDECの「JESD79-3」がリリースされたのは2007年6月。DDR3はDDR2の倍速なので、当初は実現が難しいと言われた(図1)。

図1 2006年4月18~19日に開催された「JEDEX San Jose 2006」でSamsung Semiconductorのジェシー・チャン氏の発表

資料から。1066MHzは2枚挿しで問題無いが、1333MHzだとギリギリ、1600MHzは1枚ならOKという当時の実験結果を発表した。

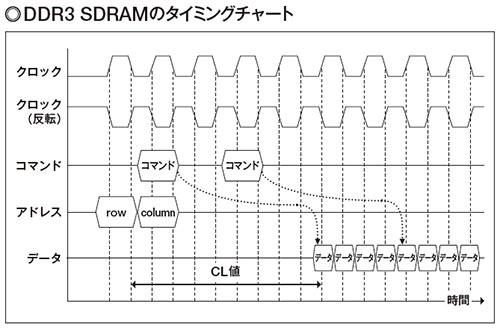

DDR3では、①クロックの引き上げ②電圧の引き下げ③8nプリフェッチ④Flybyトポロジー、が採用された。クロックはDDR2同様、倍速のクロック信号が供給される(図2)。②の電圧は1.8Vから1.5Vに引き下げられた。信号の高速化と消費電力の低下を狙った。③の8nプリフェッチは、例によってDRAMセル自体の高速化が難しいためだ。例えばDDR3-800なら、DRAMセルは100MHzで動く。

図2 タイミングチャート自体はDDR/DDR2と変わらない。メモリー自体の性能があまり変わらない状況で、同時プリフェッチを増やすことで性能を倍増させてきた。