DRAMはRAS#/CAS#/WE#という3本の信号線と、row/columnに多重化したアドレス線でアクセスする。最初の仕組みは冗長で、アクセス方法の改善で効率化できる。効率化の最初の試みが、FastPage Modeである。

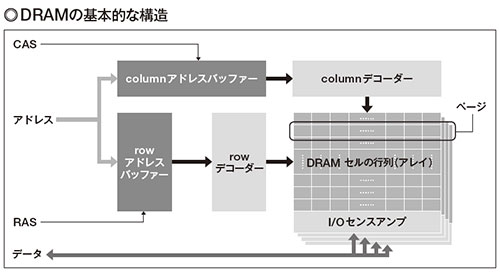

DRAMの内部はアドレスをrowとcolumnに分けるのに合わせ、DRAMのセルも行列状に配置される(図1)。FastPage Modeでは、同じrowアドレス(行アドレス)の1列を「ページ」として、アクセスを高速化した。

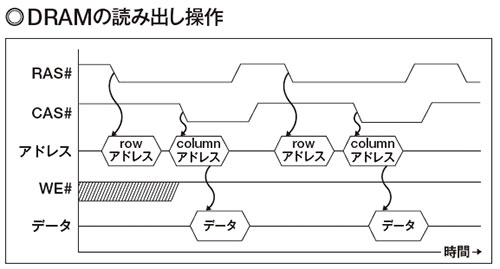

従来型のDRAMは、①RAS#を有効にすると同時にアドレス線にrowアドレスを入力②一定時間後、CAS#を有効にして、同時にcolumnアドレスを入力③一定時間後、DRAMセルから読み出されたデータがデータ線に出力、という手順でアクセスする(図2)。メモリーアクセスは連続することが多いが、連続したアドレスのデータを呼び出す場合でも、①~③の手順を繰り返す。

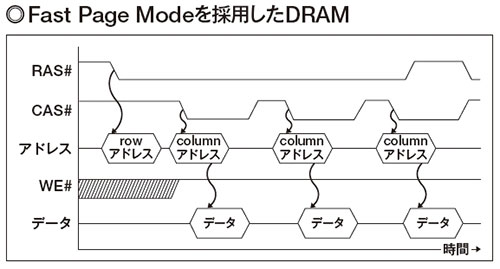

しかし連続したアドレスのデータは、多くの場合rowアドレスは一定で、columnアドレスだけが変わる。これならrowアドレスは共通なので、指定しなくてもよい。

そこで生まれたのがFast Page Modeである(図3)。通常のDRAMと①は同じだが、②~③だけを繰り返す。これにより、読み出しのアクセス効率が大幅に上がり、相対的に性能が上がる。

Fast Page Modeは、DRAMに複雑な回路を追加せずに実装できたため、あっという間に広く普及した。