「28nm世代のLSI製造技術を使いながら,1世代先となる20nm世代相当の大規模FPGAを実現できる」(米Xilinx, Inc., Senior Vice President, Chief Technology OfficerのIvo Bolsens氏)─。同社は,28nm世代のFPGAチップ4枚を1パッケージ化した,200万ロジック・セルのFPGA製品「Virtex-7 LX2000T」を開発した。2011年後半に出荷する。

200万ロジック・セルは,同じ28nm世代の製造技術を使う1チップFPGAに比べて約2.8倍の規模があり,次世代の20nm世代品に匹敵する。ASICの回路規模に換算すると約3000万ゲートである。「機器設計者は今回のFPGAを1チップ品と同等に扱える」(Bolsens氏)。Xilinx社はFPGAの大規模化によって,ASICの置き換えをさらに加速したい考えだ。

Siインターポーザで高速化

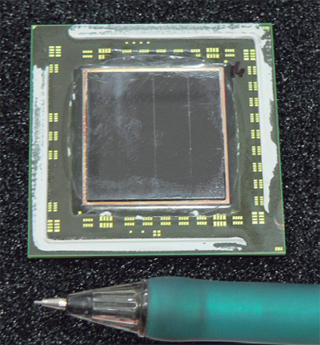

大規模FPGA製品の実現の決め手となったのが,複数のFPGAチップを1パッケージに収める「Stacked Silicon Interconnect」技術である。この技術の特徴は大きく三つある。第1に,高密度のSiインターポーザ上にマイクロバンプを使ってチップを実装し,チップ間の配線長を大幅に短縮したこと(図1)。第2に,直径25μm,ピッチ45μmのマイクロバンプを使い,チップ間の配線数を3万5000本に増やしたこと。第3に,Siインターポーザの電源/接地/信号配線と裏面のC4バンプをCu-TSV(Si貫通ビア)でつなぎ,電源の安定供給などを可能にしたことである。